## Electrical characteristics of silicon nanowire transistors fabricated by scanning probe and electron beam lithographies

## Y. K. Ryu, M. Chiesa and R. Garcia.

Instituto de Ciencia de Materiales de Madrid, CSIC, c/ Sor Juana Inés de la Cruz, 3, 28049 Madrid, Spain email: yukyoung.ryu@csic.es

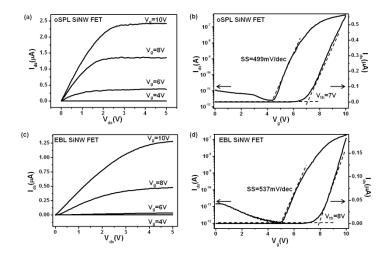

Silicon nanowire (SiNW) Schottky barrier field effect transistors have been fabricated by oxidation scanning probe (oSPL) and electron beam (EBL) lithographies [1]. From their transfer curves (see Fig. 1) it has been extracted on/off current ratios about  $10^5$ , electron mobilities about  $200 \text{ cm}^2/\text{V}$  s and subthreshold swings about 500 mV/dec for both methods, similar values to those reported from bottom-up methods. The estimation of the electron mobility requires taking into account the real geometry of the nanowire-dielectric-back gate capacitor system. In the present work, considering that the nanowire shape is trapezoidal and it is surrounded by two different dielectrics, air ( $\epsilon_{air}$ =1) and silicon dioxide ( $\epsilon_{ox}$ =3.9), we obtain a numerical value of the capacitance (finite element simulations) of 0.69 fF, that falls into the boundaries given by the parallel plate and cylinder on infinite plane models, respectively, 0.2 fF and 0.85 fF. The comparison of the electron mobility and subthreshold swing of the devices fabricated by oSPL and EBL shows that the device performance is not affected by the top-down fabrication method; both give transistors with similar electrical features, although oSPL lithography generates nanowires with smaller channel widths. The compatibility of top-down methods with CMOS procedures, the good electrical properties of the nanowire devices and the potential for making sub-10 nanowires, in particular by using oxidation scanning probe lithography [2], makes those methods attractive to fabricate sophisticated devices such as highly sensitive nanowire-based biosensors [3].

This work has been supported by EC FP7 project SNM.

Figure 1. Output and transfer curves of SiNW transistors. (a) Output curves of a device fabricated by oSPL. (b) Transfer curves of the device characterized in (a). (c) Output curves of a device fabricated by EBL. (d) Transfer curves of the device characterized in (c).

- [1] Y. K. Ryu, M. Chiesa and R. Garcia, Nanotechnology 24, 315205 (2013)

- [2] J. Martinez, R. V. Martinez and R. Garcia, Nano Lett., 8 3636 (2008)

- [3] M. Chiesa, P. P. Cardenas, F. Otón, J. Martinez, M. Mas-Torrent, F. Garcia, J. C. Alonso, C. Rovira and R. Garcia, *Nano Lett.*, **12** 1275 (2012)